半導体の微細化技術の進展によって、チップの高集積化、高速化、低消費電力化が年々進んでおり、電子機器の小型化・高機能化や高性能化を牽引する大きな推進力となっています。

しかし一方、このことは実装方式、プリント回路、プリント配線板に対し大きく影響を与えており、チップを効率よく安定的に回路接続するため、プリント配線板は近年急速に進化しています。

また、実装とは、超極微細回路を有するチップの入出力信号を実際に使用できる大きさまで機能を落とさずに拡大する手法と解釈され、実装によって回路素子を接続して電子回路モジュールとなり、電子機器を構成しています。

よって、高集積化、高速化されたチップの特性を引き出すためには配線密度が高い基板が必要となっています。近年、多ピン化や狭端子ピッチ化およびチップの微小化は年々加速する一途であり、これを搭載する半導体パッケージ用基板には、さらなる配線の微細化や高密度化、スルーホールピッチの狭幅化など、これまで以上に高い技術と信頼性が要求されています。

当社といたしましては、半導体業界の一員として多様化、高度化する顧客ニーズに対応するためにパッケージ基板の新製品、新工法、生産性向上のための製造技術などに関する研究開発に取組み、今後も得意とする薄型化、高密度化技術に磨きをかけるとともに、将来的にこれまで以上に多様化、高度化する顧客ニーズに応える新技術、新工法の研究・開発を基本方針として研究開発活動を行ってまいります。

1. ファインパターン形成

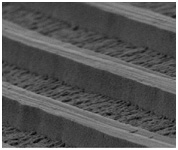

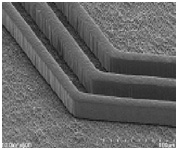

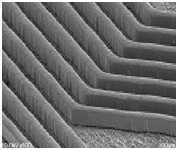

- 基板の微細化は近年著しい進展を遂げています。当社では従来工法であるサブトラクティブ法(※1)による微細化を追求しながら、近年その有効性が確立しつつあるセミアディティブ法(※2)による微細化技術を研究しております。

現在、当社は研究開発レベルでL/S=15/15umの微細化を達成しています。

L/S=25/25um

L/S=20/20um

L/S=15/15um

- ※1サブトラクティブ法

樹脂基板上に銅の薄層を形成した銅張り積層板上に、ドライフィルム層を形成、回路パターンを印刷した後、エッチング処理を施し回路以外の部分に張られた銅を除去することによって銅の回路パターンを形成する方法。 - ※2セミアディティブ法

銅箔を張っていない絶縁板の表面に薄く無電解銅メッキを施し、次にレジストを塗布、その後、導体パターン部だけに電解銅メッキを厚く施し、メッキ後、レジストを剥離してからエッチングを行うことにより導体パターンを形成する方法。

2. 微細穴あけ加工

- 電子機器の小型・薄型・軽量化が進む中、ビルドアップ多層半導体パッケージ基板においても、ますます回路の微細配線化やスルーホールピッチの狭幅化の要求が高まっています。

基板はコア層にスルーホールを有しており、これが配線幅に比べて大きな投影面積を有している場合、細線化により導体抵抗が増加した信号線が接地間容量を装荷させるために、伝送特性の劣化が更に大きくなるものと考えられています。 当社といたしましては、より微細な穴あけ技術を確立させ、課題解決をはかります。 - 開発ターゲット: 穴径30-50um

※最先端レーザーを利用し開発中

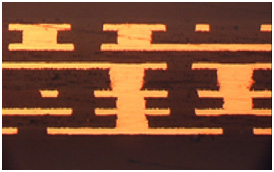

3. 極薄多層板

- パッケージ基板は高い配線密度の要求に対応するため、ビルドアップ構造が必要になります。チップの小型化にともないビルドアップ構造の多層化基板では、板厚の薄板化、配線の微細化が必要になります。

- 当社といたしましては、電気的な課題を解決した多層板の極薄化に取組んでおります。

- 開発ターゲット: 総板厚180um(4層板)

※極薄コア材、極薄プリプレグを利用

1/2/1 B/U 4層基板

2/2/2 B/U 6層基板